## Enhancing the Move framework

### Endianness port and Immediates handling

Ivo Janssen

Laboratory of Computer Engineering Faculty of Informationtechnology and Systems Delft University of Technology P.O. Box 5031, NL-2600 GA Delft, The Netherlands

May 11, 2001

#### Delft University of Technology Faculty of Informationtechnology and Systems

| Туре            | : | Master's Thesis                         |

|-----------------|---|-----------------------------------------|

| Number of pages | : | 104                                     |

| Date            | : | May 11, 2001                            |

|                 |   |                                         |

|                 |   |                                         |

| Lab./Dept.      | : | Laboratory of Computer Engineering      |

| Code number     | : | 1-68340-28(2001)-01                     |

| Author          | : | Ivo Janssen                             |

| Email           | : | janssen@cardit.et.tudelft.nl            |

| Title           | : | Enhancing the Move framework            |

|                 |   | Endianness port and Immediates handling |

| Supervisor      | : | Dr. H. Corporaal                        |

| Mentors         |   | Ir. A. Cilio                            |

|                 |   | Ir. H. Schot                            |

|                 |   |                                         |

Vail's Second Axiom: The amount of work to be done increases in proportion to the amount of work already completed.

## Enhancing the Move framework

Endianness port and Immediates handling

### Abstract

At the laboratory of Computer Engineering of the Faculty of Informationtechnology and Systems of the Delft University of Technology, research has been done in automating the design process of application specific processors (ASPs). Within this so-called MOVE project a MOVE framework was developed which shortens the design time of ASPs. With this MOVE framework a MOVE processor can be designed. The MOVE processor architecture is a VLIW-like transport triggered architecture (TTA). The main advantages of this architecture are its flexibility and scalability.

The software framework includes a generic front-end compiler, GCC and its tools, and a back-end compiler. Research and implementation has been done on the whole framework to make the architecture both host-endianness independent and target-endianness independent. Also, work has been done on the back-end to make it possible to schedule long immediates (immediates which do not fit in the fixed-width instruction) into the VLIW-like instruction stream.

To make the framework endianness independent, the GNU front-end was altered to output either big-endian or little-endian code. The back-end, our in-house developed scheduler and simulator, was altered to compile and run correct on little-endian and big-endian hosts, and the back-end was altered to be able to read the different binaries made by the front-end and to be able to schedule and simulate the code correctly, independent of the host.

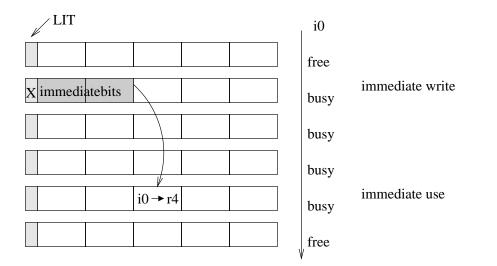

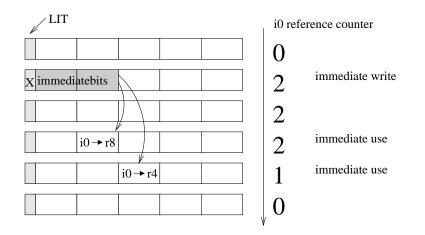

To schedule long immediates in the instruction stream, an algorithm to schedule these concurrently with the rest of the code has been constructed and data structures to hold the state of the immediates have been added to the scheduler. Where immediates used to be scheduled in dedicated immediate fields concatenated to the normal instruction word, now the immediates are scheduled in normal, otherwise unoccupied move slots. Care was taken that the routines and data structures do not interfere with already existing other algorithms in the scheduler. The algorithm increased the cycle count by several percents, but made dedicated immediate fields, that can take up 20% of the instruction word length, obsolete.

## Contents

| A  | bstrac  | et       |                                   | v    |

|----|---------|----------|-----------------------------------|------|

| Ta | ble of  | f conten | ts                                | vii  |

| Li | st of f | ìgures   |                                   | xi   |

| Li | st of a | algorith | ms                                | xiii |

| Ι  | Pro     | logue    |                                   | 1    |

| 1  | Intr    | oductio  | n                                 | 3    |

|    | 1.1     | Endian   | ness independence                 | 4    |

|    | 1.2     | Long I   | mmediates                         | 4    |

|    | 1.3     | Overvi   | ew of the rest of the thesis      | 5    |

| 2  | The     | MOVE     | Framework                         | 7    |

|    | 2.1     | The M    | OVE framework                     | 7    |

|    |         | 2.1.1    | Transport triggered architectures | 9    |

|    |         | 2.1.2    | Optimizer                         | 10   |

|    |         | 2.1.3    | Hardware subsystem                | 11   |

|    |         | 2.1.4    | Software subsystem                |      |

|    | 2.2     | Conclu   | isions                            | 14   |

#### **II** Endianness

| 3  | Ove  | view on endianness                                 | 1' |

|----|------|----------------------------------------------------|----|

|    | 3.1  | Endianness in general                              | 1′ |

|    | 3.2  | Solutions                                          | 19 |

|    |      | 3.2.1 Software solutions                           | 19 |

|    |      | 3.2.2 Changing and detecting endianness            | 2  |

|    |      | 3.2.3 Hardware solutions                           | 2  |

|    | 3.3  | Host endianness                                    | 2  |

|    |      | 3.3.1 Example                                      | 2  |

|    | 3.4  | Target endianness                                  | 2  |

|    |      | 3.4.1 Example                                      | 2  |

| 4  | End  | anness implementation                              | 2  |

|    | 4.1  | The MOVE framework                                 | 2  |

|    | 4.2  | The MOVE front-end                                 | 2  |

|    |      | 4.2.1 GCC                                          | 2  |

|    |      | 4.2.2 Assembler, linker and auxiliary binary tools | 2  |

|    |      | 4.2.3 System libraries                             | 3  |

|    | 4.3  | The MOVE back-end                                  | 3  |

|    |      | 4.3.1 Binary reader                                | 3  |

|    |      | 4.3.2 Scheduler                                    | 3  |

|    |      | 4.3.3 Simulator                                    | 3  |

|    |      | 4.3.4 Binary writer                                | 3  |

|    | 4.4  | Conclusions                                        | 3  |

|    |      |                                                    | 5  |

| II | I In | mediates                                           | 3  |

| 5  | Imn  | ediates overview                                   | 3  |

| 5  | 5.1  | What are immediates                                | 3  |

|    | 5.2  | Immediates in other architectures                  | 3  |

|    | 5.2  | 5.2.1 CISC                                         | 3  |

|    |      | 5.2.2 RISC                                         | 3  |

|    |      | 5.2.3 VLIW                                         | 3  |

|    | 53   |                                                    | 4  |

|    | 5.5  | 5.3.1 Existing implementation                      | 4  |

|    |      | 5.3.2 Possible solutions                           | 4  |

|    |      | 5.3.3 Requirements of a new implementation         | 4  |

| 6  | The  | resource variant                                   | 4  |

| U  | 6.1  | Internal workings of the MOVE scheduler            | 4  |

|    | 0.1  | 6.1.1 GCC front-end                                | 4  |

|    |      | 6.1.2 Scheduler                                    | 4  |

|    |      |                                                    | 4  |

|    |      |                                                    |    |

|    |      | 6.1.4 Binary writer                                | 4  |

15

47

|    | 6.2  | The res  | source variant                  | 48 |

|----|------|----------|---------------------------------|----|

|    |      | 6.2.1    | GCC front-end                   | 49 |

|    |      | 6.2.2    | Binary reader                   | 50 |

|    |      | 6.2.3    | Mach file                       | 50 |

|    |      | 6.2.4    | Data structures                 | 52 |

|    |      | 6.2.5    | Scheduler algorithms            | 53 |

|    |      | 6.2.6    | Simulator algorithms            | 60 |

|    |      | 6.2.7    | Binary writer                   | 61 |

| 7  | Lon  | g immed  | diates review                   | 65 |

|    | 7.1  | Perform  | mance review                    | 65 |

|    |      | 7.1.1    | The benchmark suite             | 65 |

|    |      | 7.1.2    | The results                     | 66 |

|    |      | 7.1.3    | Conclusions                     | 70 |

|    | 7.2  | Future   | work                            | 70 |

|    |      | 7.2.1    | Exploration                     | 70 |

|    |      | 7.2.2    | Immediate sharing               | 71 |

|    |      | 7.2.3    | Region scheduling of immediates | 72 |

|    |      | 7.2.4    | Conclusions                     | 73 |

| 8  | The  | pseudo-  | -move variant                   | 75 |

|    | 8.1  | -        | nentation                       | 75 |

|    | 8.2  | -        | ative comparison                | 77 |

|    | 8.3  |          | tative comparison               | 79 |

|    | 8.4  | Conclu   | isions                          | 80 |

|    |      |          |                                 |    |

| IV | ' Ej | pilogue  |                                 | 83 |

| 9  | Con  | clusions | s and recommendation            | 85 |

|    | 9.1  | Conclu   | usions                          | 85 |

|    |      | 9.1.1    | Endianness                      | 85 |

|    |      | 9.1.2    | Long Immediates                 | 86 |

|    |      | 9.1.3    | General                         | 86 |

|    | 9.2  | Recom    | mendations                      | 87 |

|    |      | 9.2.1    | Endianness                      | 87 |

|    |      | 9.2.2    | Long Immediates                 | 87 |

| A  | End  | ianness  | related data structures         | 89 |

|    | A.1  | SimMe    | em                              | 89 |

| В  | Lon  | g immed  | diate related data structures   | 93 |

|    |      |          |                                 |    |

| С  | Mac    | hine description files | 97  |

|----|--------|------------------------|-----|

|    | C.1    | mach.small             | 97  |

|    | C.2    | mach.pcomp             | 98  |

|    | C.3    | mach.one               | 100 |

|    | C.4    | mach.big               | 101 |

| Bi | bliogr | aphy                   | 103 |

# List of Figures

| 2.1 | MOVE framework overview.                                                | 8  |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | General structure of a TTA                                              | 9  |

| 2.3 | Possible solutions and Pareto points                                    | 10 |

| 2.4 | The hardware subsystem.                                                 | 11 |

| 2.5 | The software subsystem.                                                 | 12 |

| 2.6 | Relations between the ported GNU compiler, the assembler and the linker | 13 |

| 4.1 | The front-end on both endianness platforms                              | 27 |

| 5.1 | PA-RISC2.0 instruction format                                           | 38 |

| 5.2 | Sample IA-64 instruction stream; 128 bits wide                          | 40 |

| 5.3 | Dedicated immediate slot in instruction word                            | 41 |

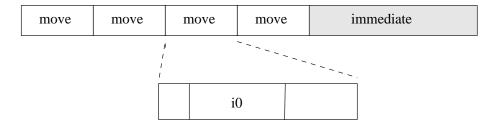

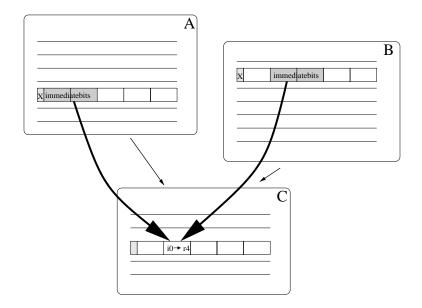

| 6.1 | Scheduling of long immediates                                           | 50 |

| 7.1 | Sharing of long immediates                                              | 72 |

| 7.2 | Importing of long immediates                                            | 73 |

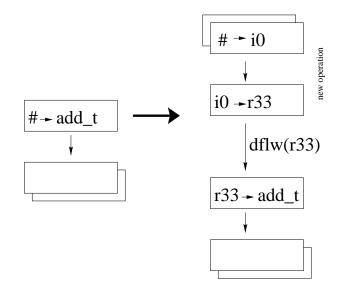

| 8.1 | Transformation to immediate operation                                   | 76 |

# List of Algorithms

| 1  | FindImmMoveBus 44                                         |

|----|-----------------------------------------------------------|

| 2  | Scheduler algorithm                                       |

| 3  | SimulatePar(Proc*, int offset)                            |

| 4  | OutputBinary(ostream &, Insn *)49                         |

| 5  | Overall scheduling of long immediates                     |

| 6  | FindImmMoveBus(move, cycle)                               |

| 7  | ScheduleLImm(read_node, ireg) 56                          |

| 8  | FindIRegWriteBus(write_cycle, read_cycle, ireg) 57        |

| 9  | IsLImmControlValidSubset(LIT super, LIT sub, ireg cur)    |

| 10 | AssignMBusses(RTabEntry) 58                               |

| 11 | LookupIRegWrite(read-node, bool release, cycle, snode) 60 |

| 12 | SimulatePar(Proc*, int offset)                            |

| 13 | OutputBinary(ostream &, Insn *)                           |

| 14 | BuildLongImmediates (*Move) 78                            |

| 15 | AssignLongImmediates                                      |

Part I

Prologue

# 1

### Introduction

This chapter gives a short introduction to the various topics covered in this thesis.

At the laboratory of Computer Engineering of the Department of Electrical Engineering, Delft University of Technology, research has been done in automating the design process of application specific processors (ASPs). ASPs represent a huge part of the microprocessor market, as they are used in increasingly popular embedded systems.

One of the largest part of the costs of an ASP is its design time. To shorten this design cycle, this laboratory has been developing an automated design framework based on the *Transport Triggered Architecture* paradigm. The concepts behind TTAs were developed in the same research group, and proved themselves to be especially suited for the ASP synthesis. For an in depth description of the move framework, please read chapter 2.

Several for-profit companies have been interested to take the Move framework principles and use them in their own products. One of them is NEC Computer and Communications Research Labs (CCRL) in Princeton, New Jersey, USA <sup>1</sup>, later spun off into the independent company Eulix Networks. While developing a programmable communications processor, they needed a core that was both flexible in its interface and functionality while having a short design cycle. The MOVE framework was chosen to implement this core. The requirements as posed upon the MOVE framework by the communications processors specifications included, amongst others, a little-endian version of the MOVE core, support for long immediates, support for some special function units (SFUs) attached to the MOVE core, support for 64bit loads and stores, support for global registers, and support for an interface to the co-design simulator of the processor.

In September 1999, I was asked by my professor, dr. H. Corporaal, to join the development group in New Jersey to work primarily on two of these issues, namely the support for long im-

<sup>&</sup>lt;sup>1</sup>see http://www.ccrl.nj.nec.com/

mediates and the support for endianness independence. I also did some work on other problems related to the integration of the MOVE core into the communications processor, but they will not be discussed here as they fall outside the scope of my master's thesis.

#### **1.1 Endianness independence**

The communications processor, as developed by Eulix Networks, deploys several on-core traffic control units as well as some busses, e.g. a standard PCI bus for external host-communications. Since these were all developed as little-endian modules, it was natural for the MOVE core to be little-endian, too. Traditionally, MOVE has been a big-endian target, developed and simulated on big-endian hosts, like HP's HPPA and Sun's Sparc architectures. Lately, development in the research laboratory has been shifted towards more common, cheaper, x86 platforms, running the Linux operating system. The x86 is a little-endian platform.

All these factors lead to the conclusion that the traditionally big-endian-host/big-endiantarget architecture of MOVE needed to be extended to handle all four permutations of host and target endianness.

#### **1.2 Long Immediates**

Traditionally, MOVE has been primarily a research concept, with few actual realized hardware prototypes. As such, the limitation that the width of an immediate in bits needed to be shorter than the (fixed-width) instruction width of an instruction slot, could be easily overcome, since the simulator didn't need to work on the actual bits of the binary, but on a symbolic representation of the scheduled program in memory.

In the cases where a chip was actually realized, short term solutions were devised. One of them was to use a two-step stage, where an instruction containing an immediate was always followed by an instruction slot that did not contain an instruction but the value of the immediate. The program counter was incremented by two instead of one in this case.<sup>2</sup>. This was a good solution since the scheduling freedom was low anyway, due to the fact this particular MOVE instance had only 1 bus, but a bad one if the MOVE architecture would define multiple busses, since then it would be more advisable to schedule them into empty slots that are inherently present in VLIW scheduled instruction words.

Another solution was to add a dedicated immediate field at the end of the VLIW instruction word, that could never contain an instruction but only an immediate. Downside of this solution is that an instruction word would always contain one or more immediate fields, and that in case there was no instruction with an immediate present, bits would be wasted, which is a significant factor when it comes to low-cost embedded processors.

Above observations led to the conclusion that a new way to schedule immediates needed to be implemented. An implementation that would not waste bits but would try to schedule an immediate in unused instruction in the instruction word stream, thus minimizing the code size.

<sup>&</sup>lt;sup>2</sup>This solution was implemented in the MicroMove [Jan97] processor by TNO-FEL, The Hague, Netherlands

#### **1.3** Overview of the rest of the thesis

First, chapter 2 will describe the Move project, in order to have a good understanding of the principles of the Move framework.

The remaining of this thesis will further address the main two topics of this thesis.

Chapter 3 will address the ideas and difficulties behind endianness of both host-endianness dependencies and target-endianness dependencies. Chapter 4 will explain how these problems were addressed in making the Move framework both host-endianness as well as target-endianness independent.

Chapter 5 will explain the rationale behind long immediates in the Move framework. Chapter 6 will address the implementation of long immediate support in the Move framework. Chapter 7 will review these adaptations, and a quantitative and qualitative analysis will be given, as well as a comparison with a functionally similar approach to long immediates encoding and implementation in a different research group.

Finally, chapter 9 will draw conclusions on the results and will give some recommendations for future work on this subject.

# 2

## The MOVE Framework

Due to the decreasing feature size of VLSI technology, the amount of hardware which can be integrated into a single chip increases. As a result, future processor chips may execute tens of operations concurrently. Many applications can profit from these huge amounts of hardware parallelism by designing an application specific instruction set processors (ASIP). Two problems emerge however: (1) the design space of ASIPs is very large; it is difficult to chose a satisfactory solution, and (2) the design complexity increases and therefore design cycle gets too long.

To alleviate these problems a design trajectory based on a *templated, transport triggered architecture* (TTA) has been developed. Using a restricted, but still very large, design space it is possible to automate the design trajectory based on a quantitative analysis of many design points. A key aspect of TTAs is the reduction of the on-chip data transport requirements; this may result in a better cost-performance ratio of the realized ASIPs. In this chapter we discuss an automated design process for ASIPs using the *MOVE framework*.

The chapter is structured as follows: Section 2.1 explains the MOVE framework, and discusses briefly how TTAs operate. Then, in section 2.2 several conclusions are drawn.

#### 2.1 The MOVE framework

Designing ASICs based on templated application-specific instruction set processors (ASIPs) is an attractive solution that offers flexibility and a short design time while still retain part of the advantages of ASICs. The design process consists of finding the right architecture parameter values for the given application, such as the operation set, the amount of instruction level parallelism, and the sizes of the register files. Also, additions of special function units that can map a complex task into one single optimized instruction are possible. The quality of a solution depends on the offered performance and the implementation costs.

The synthesis framework presented in this section uses an architecture design space based on a *transport triggered architecture*, or TTA. This architecture is of the *instruction level parallel* type; it resembles the well known VLIW architectures. However, a key difference is that TTAs are programmed by specifying data transports instead of operations. This gives an finer level of control to the code generator, and allows for a more efficient use of hardware resources. Although we use a TTA template for designing ASIPs, the design space is still very large. Picking a proper solution (for a specific application) from this design space requires a quantitative analysis of many design points. This search process must largely be automated in order to reduce the design time. Therefore tools are needed, not only for making the quantitative analysis of hardware and software (generated code), but also for the automated search.

The MOVE framework consists of a set of tools for hardware and software synthesis. Within the synthesis process we use an *architecture template*, i.e. processors are built according to the pattern of a TTA. A specific TTA is defined by a set of architecture parameters, like the number and type of function units, the number of register files and registers, etc. At first sight this suggests that we restrict ourselves and therefore obtain inferior solutions. In practice however, several advantages emerge. Firstly, the template building blocks are pre-designed and can therefore be made very efficient, both in area and performance. Secondly, the architecture pipelining is worked out very carefully, alleviating many timing bottlenecks; prototype realizations learned where these bottlenecks exactly are. Finally, usage of a clearly defined design space allows the design of synthesis and evaluation tools, which not only generate a combined hardware and software solution, but also allow a quantitative analysis of the design space. Also, note that the template still covers a very large design space.

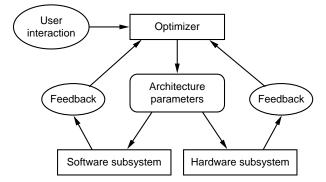

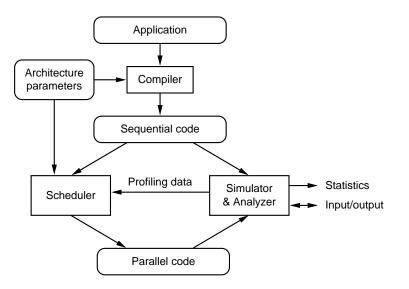

Figure 2.1: MOVE framework overview.

The synthesis of hardware and software for a given application is done using the MOVE framework; this framework produces both the layout of an ASIP and the corresponding object code to be executed on this ASIP. An overview of this framework is shown in figure 2.1. It consists of three main components:

- 1. **Optimizer** which is responsible for searching the design space and the interaction with the designer. It determines the configuration (i.e., the set of architecture parameters) to be evaluated next.

- 2. Hardware subsystem generating processor layout, and giving information on timing,

area, and power consumption.

3. **Software subsystem** generating instruction level parallel code, and giving statistical information on usage of hardware resources.

These components are detailed in following subsections. Before, we briefly describe how TTAs operate.

#### 2.1.1 Transport triggered architectures

TTAs can be compared to VLIW architectures; their instructions are horizontally encoded; i.e. each instruction has a number of fields. Whereas fields for VLIWs specify RISC like operations, for TTAs they specify the required data transports. These transports may trigger operations as side effect. Programming transports adds an extra level of control to the code generator, and enables new optimizations; in particular, it allows us to get rid of many superfluous data transports to and from the register files and to reduce the on-chip connectivity[HC94].

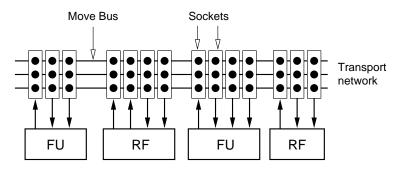

A compiler views a TTA as a collection of function units (FUs), register files (RFs), *move buses*, and *sockets*; see figure 2.2. FUs perform operations, RFs provide temporary fast accessible storage, the network of move buses performs data transports between the FUs and RFs, and sockets interface FUs and RFs to move buses. Normally, each socket is connected to a different FU input/output or RF port.

Figure 2.2: General structure of a TTA.

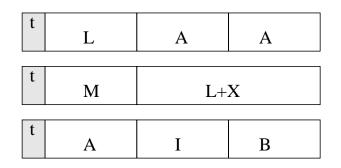

To illustrate TTA programming, consider the following three operations of an operation triggered machine, or OTA:

add r1, r2, r3 /\* r1 = r2 + r3 \*/ sub r4, r2, r6 /\* r4 = r2 - r6 \*/ st r4, r1 /\* store r4 at address r1 \*/

These operations can be translated into the following two TTA instructions:

r2->add\_o, r3->add\_t, r2->sub\_o; r6->sub\_t; add\_r->st\_t, sub\_r->st\_o;

In the first instruction the four operands of the add and subtract operations are moved from the RF(s) to the FU inputs of the FUs that perform the two operations. In the second instruction

the results of the add and subtract operations are moved from the FUs that performed them to the FU that performs the store operation. From this small example we already observe a few advantages of TTAs. The results of the add and subtract operations are not written back to the RF and the operands of the store operation are not read from the RF. The former saves RF write accesses and data transports, the latter saves RF read accesses. Since TTAs do not couple move buses and RF ports directly to FUs, as is the case for many VLIW and super-scalar architectures, the freed resources can be used for other operations. This makes that TTAs have a better hardware utilization, which implies less hardware for the same performance or more performance with the same hardware [HC94].

The interconnection network may be fully connected, as shown in figure 2.2, in which case every socket is connected to all move buses, or partially connected. A fully connected interconnection network simplifies the code generation task, but it likely results in a high bus load on the move buses which affects the achievable cycle time. Therefore, in practice the interconnection network will be partially connected and the compiler is responsible to use the available connections as well as possible.

Besides executing operations on data, TTAs need to provide immediate operands, conditional execution, and control flow changing operations. Details on these issues can be found in [Cor95b, CM91].

#### 2.1.2 Optimizer

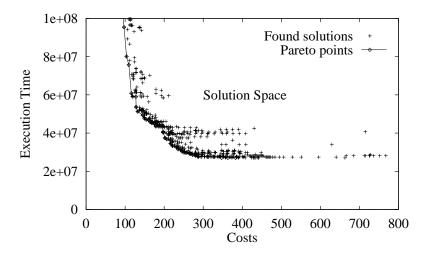

Figure 2.3: Possible solutions and Pareto points.

Two main design evaluation criteria are cost and performance, where performance is defined as the inverse of execution time. Costs may include the amount of chip area, number of pins, power dissipation, and code size<sup>1</sup>. Execution time is dependent on the number of executed operations, latencies, cache misses, and the clock cycle time. The *solution space* is given by all possible design points in the 2-dimensional cost-performance space. Figure 2.3 shows many generated solutions for a test application (described in [CH96]). As shown, the solution space is

<sup>&</sup>lt;sup>1</sup>Currently are included area and pins only.

bounded by a curve connecting so called Pareto points.

The optimizer finds its way through this search space by iteratively trying different architecture solutions, and letting the software and the hardware subsystems produce relevant information about these solutions, like cycle time, costs and number of cycles needed to run the application. Based on this information a next design point is chosen by updating the parameters. The initial architecture parameter values can be chosen freely by the user. He can also specify an evaluation function (e.g. minimize the product of costs and execution time), and the stop criteria.

#### 2.1.3 Hardware subsystem

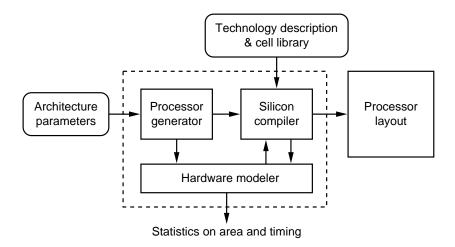

The hardware subsystem of the MOVE framework is responsible for the realization of an application specific TTA in silicon. It accepts architecture parameter values, technology information and a cell library as input, and produces a VLSI layout (e.g. in CIF format) of the generated processor as output. Figure 2.4 shows its organization.

Figure 2.4: The hardware subsystem.

The design space explorer makes use of a *hardware model* to estimate the cost of design points. The costs of FUs are based on a 32-bit data path width<sup>2</sup>, and relative to an integer FU. The minimum clock cycle time for a TTA realization is largely determined by the time needed to perform (and control) data transport.

#### 2.1.4 Software subsystem

The software subsystem is detailed in figure 2.5. It provides the user with three main tools to develop code for TTAs. These tools are:

1. A compiler (referred to also as MOVE front-end) to translate HLL (high level language) code to sequential move code

<sup>&</sup>lt;sup>2</sup>Although the hardware subsystem can generate processors for any data width, the software subsystem currently requires 32 bit integers.

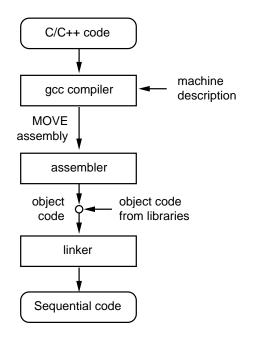

Figure 2.5: The software subsystem.

- 2. A scheduler (or MOVE back-end) to schedule the sequential code and produce parallel code for a target TTA

- 3. A simulator and analyzer to verify and evaluate both the sequential and parallel code.

The software subsystem accepts any application coded in C or C++ and translates it into text representation of MOVE parallel code for a specific TTA. The components of the software subsystem are described in detail below.

#### Compiler

The MOVE front-end is a combination of three tools: proper compiler, assembler and linker. Their relationship is depicted in figure 2.6. In order to be assured of good code quality, good HLL compatibility, support for new HLLs and an extensively debugged compiler, a port of GNU C compiler (gcc), assembler, and linker was made. These software packages are ported to produce binary sequential MOVE code for a *MOVE generic machine*. This code is sequentially ordered by instructions; each move referring to the same operation is grouped in a single instruction, resembling OTA instructions. Sequential code is used as intermediate representation of the program and is read by the scheduler.

#### Scheduler

The scheduler is the most important part of the software subsystem. Its main function is to schedule moves of sequential code, i.e. to assign FUs to operations and to assign cycles, sockets and buses to moves. The scheduler has to generate instruction level parallel code, while exploiting all the available hardware resources. To this purpose, the scheduler uses profiling data (like execution frequencies) from the simulator. Several preliminary optimizations on sequential code are also applied. The scheduler uses advanced techniques like extended basic block scheduling, software pipelining, and speculative execution, in order to enhance code motions and consequently

Figure 2.6: Relations between the ported GNU compiler, the assembler and the linker.

inter basic block parallelism [Hoo96]. All specific optimizations of TTAs (result bypassing, dead moves elimination, operand sharing) are performed during the scheduling process. The parallel code is fully parameterized on the template configuration, which is specified in a machine description file. In this file processor resources, like supported FUs, amount of registers and interconnection network are described. Profiling information is not strictly necessary, but helps the scheduler to work more efficiently.

#### Simulator

The simulator accepts either sequential MOVE code or parallel MOVE code. Its output consists of profiling information, application output and execution statistics. The simulator has three purposes in the MOVE framework:

- 1. To verify the compiler and the scheduler. It is virtually impossible to port a compiler and write a scheduler without simulating the produced code.

- 2. To evaluate architecture parameters. The results of the evaluation are cycle counts and various statistics about resource utilization and compilation events (e.g. the number of operand swaps and the number of loop scheduled using software pipelining).

- 3. To provide profiling data to the scheduler. Profiling data consist of execution counts for each basic block and each control flow edge between basic blocks in the program. With this information the scheduler can decide which code motion between basic blocks is most profitable.

#### 2.2 Conclusions

In this chapter we showed an automated design trajectory for ASIPs based on transport triggered architectures. This trajectory has two fundamental capabilities:

- 1. It maps arbitrary applications, written in C/C++, into a combination of hardware and software.

- 2. It offers the possibility to do a quantitative analysis of large parts of the design space.

The search process to find a proper solution consists of resource and connectivity optimization. Resource optimization attempts to find the cost effective set of resources. Connectivity optimization reduces the connectivity in order to reduce bus load and cycle time. As side effect it has been demonstrated that the synthesized TTAs require far less connectivity and fewer register ports than more traditional instruction level parallel architectures.

## Part II

# Endianness

# 3

## Overview on endianness

The MOVE framework historically ran on big-endian platforms like HPPA, Sparc and MIPS. With the increased popularity of Linux running on relatively cheap little-endian platforms, like the x86 platform, the need for a port of the MOVE framework to a little-endian host platform arose. At the same time, the "PcomP" implementation of the MOVE architecture was decided to be little-endian. This and the next chapter will deal with changing the MOVE framework to be running independent of the host platform's endianness, as well as changing the MOVE framework to be able to generate and simulate code for both little and big-endian targets.

This chapter will give an overview on endianness dependence itself, and how that affects implementation of tools, with the emphasis on emulation tools. Chapter 4 will discuss how the principles of this chapter are used in the port of the MOVE framework.

#### 3.1 Endianness in general

Endianness, deals with the ordering of fields within an item. Usually it means byte ordering within a halfword, word and double word. However it can also mean bit ordering within bytes. Byte ordering is the most visual, since most memory systems are byte addressable, IO works on bytes, strings are packed as bytes within words, etc. Bit ordering comes into play when structures are accessed with bitfields in a byte. The latter becomes architecturally visible when a program accesses bitfields within a byte.

The historical name "endianness" refers to the book "Gulliver's travel" by Jonathan Swift. The Lilliputians liked to break their eggs on the small end and the Blefuscudians on the big end. According to the book, ...It is computed that eleven Thousand Persons have, at several Times, suffered Death, rather than submit to break their Eggs at the smaller End. Many hundred large *Volumes have been published upon this Controversy.* The analogy is taken very well, since there is no real "correct" implementation. Both have their advantages and disadvantages.

The official definition of big-endian and little-endian is the following:

**big endian** ordering means storing the least significant byte at the most significant address.

**little endian** ordering means storing the least significant byte at the least significant address.

Consider the following 16 bytes of data in table 3.1

| address  | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 10 | 11 | 12 | 13 | 14 | 15 |

|----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| contents | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 10 | 11 | 12 | 13 | 14 | 15 |

Table 3.1: Memory as an array of bytes

If instead of considering the memory as an array of bytes, we consider the same memory contents as four 32-bit words. Then it will be shown that a little or a big endian machine have a different view on the memory. Table 3.2 will show a little-endian memory and table 3.3 will show a big-endian memory.

|    | cont | word addr |    |    |

|----|------|-----------|----|----|

| 03 | 02   | 01        | 00 | 00 |

| 07 | 06   | 05        | 04 | 04 |

| 11 | 10   | 09        | 08 | 08 |

| 15 | 14   | 13        | 12 | 12 |

Table 3.2: Little endian memory as an array of words

| word addr | contents |    |    |    |  |  |  |  |

|-----------|----------|----|----|----|--|--|--|--|

| 00        | 00       | 01 | 02 | 03 |  |  |  |  |

| 04        | 04       | 05 | 06 | 07 |  |  |  |  |

| 08        | 08       | 09 | 10 | 11 |  |  |  |  |

| 12        | 12       | 13 | 14 | 15 |  |  |  |  |

Table 3.3: Big endian memory as an array of words

In the two tables, the bytes are grouped into four byte words, which are shown in the normal Arabic form, with the most significant byte on the left. In table 3.2 the word address column was put on the right ("little end") because the computer uses the address of the least significant byte, the byte on the right, to address the word. In table 3.3, the address column is on the left ("big-end"), showing that the computer addresses the most significant byte in words operations. As a result, a little endian processor loading the 32-bit work at word address  $0 \times 000010203$ .

An important observation that has to be made is that if a certain machine is unable to access bits in a byte, the endianness with respect to bit-ordering means nothing. This is because the program has no way to access data smaller than a byte anyway, and as long as the machine stores and retrieves the data in a consistent way, it doesn't matter how exactly this is done. The same goes for a machine which is word-addressable, because words will always be fetched as a whole from memory, and it doesn't matter how those words are stored in memory.

Examples of little-endian machines are the Intel x86 family and various architectures from DEC, like the VAX, the PDP-11 and the Alpha. Examples of big-endian machines are the Sun Sparc, HPPA and the m68k architecture. Still other architectures, like the PowerPC, the MIPS and the Intel IA-64 architecture, are capable of operating in either big or little endian mode. Usually the operating system dictates the endianness that the processor is going to use during that boot.

Regarding endianness, we can divide the problem in two parts. First is the most known one, the so-called "host endianness". This kind of endianness concerns the problem of begin able to use data between platforms of different endianness. What one wants to do is, for instance, write a binary file on a big-endian platform, and read it on a little-endian platform. This is what section 3.3 discusses. Section 3.4 discusses another problem regarding endianness, the so-called target-endianness. This kind of endianness concerns the fact that a certain host should be able to process data in a certain endianness, without having that data being related to the host itself. This is a common scenario when dealing with foreign binaries. MOVE specific, this means that a certain host has to be able to process binaries, and simulate binaries, from any endianness. First we will present some solutions to handle endianness, both on the software level as on the hardware level.

#### 3.2 Solutions

#### 3.2.1 Software solutions

There are different ways to agree on an interface:

- 1. Form an endianness-independent transport layer. Certain graphics applications, like Framemaker, have an option to write the data to an endianness independent file. With Framemaker, this is the .mif-format, or Maker Independent Format. This file can be read on any platform, but is two to three times larger than the normal .doc format that Framemaker uses. Sun has its XDR (eXternal Data Representation) format [Zuk98], which, apart from endianness independence, also claims independence from various floating point implementations.

- 2. Let the data be stored/transmitted in the native endianness of the sender. This is done along with tag or header that indicates endianness. This method is deployed by the TIFF graphics format, which can either be "IBM ordered" or "Macintosh ordered". A header specifies whether the data is big ("Macintosh ordered") or little ("IBM ordered) endian. Another scenario where this principle is applicable is when dealing with binaries from a different architecture. If a binary is in a certain endianness, and it is emulated or simulated on a host machine, this host machine has to check for endianness in that 'target' architecture and handle accordingly.

3. Let the data always be a certain kind of endianness. This is the most common way to handle endianness, since it is unambiguous what the data's endianness is. This way a program only has to take into account its own endianness. This is also the way the Internet works. Data transmitted over the internet is always big-endian, and Unix systems provide the system calls ntohl(3) and htonl(3), for respectively "network-to-host" swapping and "host-to-network" swapping.

#### 3.2.2 Changing and detecting endianness

To "encode" an endianness independent layer, like in option 1, every designer is free to choose his own implementation. Option 2 and 3 only need a so-called "byte-swap" or "byte-reordering". For this "byte-swap", a very simple piece of code can be used:

What we do here is just swapping bytes 1 and 4, and bytes 2 and 3 in a word. This will indeed swap the data, and will convert tables 3.2 and 3.3 into each other. This macro is exactly the code used in the ntohl(3) and htonl(3) calls on little-endian platforms. On big-endian platforms, where there is no swap needed, since host ordering and network ordering are the same, these two calls are null-macros, a very efficient way to implement a no-operation in C or C++.

A good way to detect the endianness of a platform is the following standard piece of code:

```

long i = 0x44332211;

unsigned char* a = (unsigned char*) &i;

end = (*a != 0x11);

printf("The endianess is %s!\n", ((end==1)?"big":"little"));

```

This piece of code will fetch one byte out of the word i, by getting the byte addressed by the pointer to i. If the platform's endianness is little, the byte  $0 \times 11$  is fetched, since the *least* significant byte is stored at the most significant address, which is the pointer's address. If the platform's endianness is big, the byte  $0 \times 44$  is fetched, since the *most* significant byte is stored at the most significant address is the address to which the pointers i and a point.

#### 3.2.3 Hardware solutions

Although not in the scope of this thesis, a brief overview on hardware solutions to the endianness problem are discussed. If there is no way to have software do byte-swapping, the hardware has to do this. A common principle to do this is to give the system multiple views on the address space where the endianness-dependent devices, like memory or graphics processor, reside. These various views are called *apertures*. For example, a PCI based graphics adapter that internally uses a little endian processor can provide two apertures (ranges of addresses) for its frame buffer. Accesses to the little endian aperture store the data as presented on the bus directly into the frame buffer; accesses to the big endian aperture swaps the data bytes before storing them. Thus, an

application running on a big endian processor can simply access the big endian aperture and store its big endian data just as if it were running on a little endian processor. The device takes care of swapping the data in hardware as necessary.

## **3.3 Host endianness**

Host endianness concerns the way data can be kept portable across platforms. This section will concentrate mainly on files, although its principles can easily be extended to other forms of interoperatibility, like shared memory between a graphics processor and a CPU, or interarchitecture buses (PCI, SCSI). Regarding Move, this means that solution 3 from section 3.2.1 is used: Let the data on disk always have the same endianness. This way the only check a program has to do is its own endianness.

#### 3.3.1 Example

As an example of host-endianness, we will explain the profiling code in the scheduler. The profiles, including frequency counts and memory dependencies, are target-independent data. Therefore, they are stored on disk in a pre-defined endianness. In this case this is big-endian.

The functions Prog::SaveProfile and Prog::LoadProfile are responsible for writing and reading the profiles. Therefore the following code can be found:

```

for(p = proc; p; p++)

{

for(b = p->blck; b; b++)

{

#if HOST_LITTLE_ENDIAN

f = SwapEndianess(b->freq);

#else

f = b->freq;

#endif

file.write((char *) &f, sizeof(double));

}

}

```

For each procedure, and each block in that procedure, an integer b->freq exists, indicating the frequency of that basic block during execution. Because agreed was that all data on disk was big endian, a byte swap is performed, governed by the predefine HOST\_LITTLE\_ENDIAN. The function SwapEndianess performs the actual byte swap in the word b->freq.

## **3.4** Target endianness

Target endianness concerns the portability of foreign code on a platform of random endianness. This is especially relevant here, since any platform, either big or little, should be able to omit, schedule and simulate binaries from any MOVE architecture. Now it is, contrary to host-endianness, important to keep the endianness of a file intact while reading and writing. This means we take on option 2 as presented in the list of subsection 3.2.1. This option says that the

endianness of a certain file can depend. This means that the program has to know up front what kind of file it is dealing with. Regarding Move, this means that the tools have to know what kind of endianness the target-binary has. Since the host-endianness still has to be taken into account, the rules for swapping get more complicated. Table 3.4 shows all cross-combinations possible. For swapping, the macro as presented in subsection 3.2.2 can be used.

|             | target<br>big | target<br>little |

|-------------|---------------|------------------|

| host big    | no swap       | swap             |

| host little | swap          | no swap          |

Table 3.4: Endianness swap depending on host and target

#### 3.4.1 Example

As an example of target endianness, we take the reading of the text segment of the serial binary. The text segment is "target-dependent", that means that the serial binary can contain either Move code for a little-endian Move architecture or a big-endian Move architecture. The scheduler is compiled with an option that indicates what kind of target-endianness is should be capable of handling. This is defined in the config.h file of the scheduler:

```

#define __pcomp___

#ifdef __pcomp___

#define TARGET_LITTLE_ENDIAN 1

#define TARGET_BIT_FIELDS_LEFT_TO_RIGHT 0

#else

#define TARGET_LITTLE_ENDIAN 0

#define TARGET_BIT_FIELDS_LEFT_TO_RIGHT 1

#endif

```

By setting the \_pcomp\_ define, the target-endianness is known throughout the whole scheduler. Then we add some extra defines that indicate whether the target-endianness is different from the host-endianness (remember that the host-endianness is already stated in the HOST\_LITTLE\_ENDIAN defines, derived from the presence of the compiler-required defines \_\_386 and \_\_sun.

```

#if HOST_LITTLE_ENDIAN && TARGET_LITTLE_ENDIAN

#define SWAP_ENDIANESS 0

#elif HOST_LITTLE_ENDIAN && !TARGET_LITTLE_ENDIAN

#define SWAP_ENDIANESS 1

#elif !HOST_LITTLE_ENDIAN && TARGET_LITTLE_ENDIAN

#define SWAP_ENDIANESS 1

#elif !HOST_LITTLE_ENDIAN && !TARGET_LITTLE_ENDIAN

#define SWAP_ENDIANESS 0

#endif

```

Now we can proceed to the file exec.h, which implements the AOut class that reads in the serial binary. Now we can read in the whole text segment. class AoutMove represents a move instruction in the binary.

```

AoutMove* text = (AoutMove *) &image[N_TXTOFF(*exec)];

#if SWAP_ENDIANESS

SwapEndianess(text, exec->a_text);

#endif

```

We simply map the whole binary (represented by image) to the text array. Now the only thing left to change is the ordering of the bytes in a word. Since this ordering is dependent on both the host ordering as the target ordering, the SWAP\_ENDIANESS define governs whether a swap is needed, pursuant to table 3.4.

# Endianness implementation

This chapter will explain how the MOVE framework was made endianness-independent. The previous chapter explained the issues concerning endianness, and this chapter will deploy the guidelines from that chapter on the MOVE framework, to make it host-platform independent as well as move-target independent.

# 4.1 The MOVE framework

The MOVE framework consists of roughly two parts: the front-end and the back-end. This can be visualized in figure 2.5. The front-end consists of a standard freely available compiler, the GNU C Compiler, including its tools like assembler, linker and auxiliary tools. This compiler can be easily ported to other architectures by means of writing a new architecture plug-in. The tools related to the compiler, the so-called binary tools, include an assembler, linker and various other tools that operate on the binary. These tools were ported to the MOVE architecture by rewriting the "m68k" assembly format to fit the MOVE specification. Lastly, a system library, also called the C-library, is needed. This library does not need any MOVE specific changes, but it does have some endianness dependencies that need to be resolved. The adaptations needed to make the front-end endianness independent can be found in section 4.2

The back-end consists of the scheduler tools, including a simulator, scheduler and various auxiliary tools that help the simulator and the scheduler, like a design-space explorer, a call-graph visualizer and a tool to view the assembly code in a human readable form. The adaptation needed to make the back-end endianness independent can be found in section 4.3

The approach taken was to make the whole framework first host-endianness independent. This alone would allow us to deploy the MOVE framework on Linux platforms instead of Sparc platforms, even if there was no problem of target endianness (i.e. the Move architecture has only one endianness, e.g. big, and only the endianness of the host has to be taken into account). This port was done in such a way, that further work on making the framework target-endianness independent, would be straightforward and trivial. Another requirement was that the host-endianness dependencies would be compile-time invisible, so that there would be no need to set compile-time switches to help the framework determine what kind of host platform is was compiled on. This was achieved through the use of the predefines that the compiler sets: e.g. \_\_i386 is set during building and installation on an Intel platform.

Target endianness was implemented in such a way that a single switch in the two Makefiles is sufficient, one for the front-end and one for the back-end. This would require a recompile for each target. This was considered not a problem, since the MOVE framework's directory layout also included a directory for pre-compiled libraries, which would be target-endianness dependent anyway. A new tree for either little or big-endian targets, including compiler-binaries and libraries for each target, is then created.

First, some defines are set to indicate the host and target endianness:

- If the host platform is big-endian (check \_\_sun flag, a preprocessor predefine that is always set on Sparc machines), then the define HOST\_BIG\_ENDIAN is set to 1 and the define HOST\_LITTLE\_ENDIAN is set to 0. Else, the host platform is little endian, and both defines get their inverse value.

- If the target architecture is little-endian (check setting in config.h for the back-end, a Makefile directive in the front-end) then the define TARGET\_LITTLE\_ENDIAN is set to 1 and the define TARGET\_BIG\_ENDIAN is set to 0. Else, the target architecture is big endian, and both defines get their inverse value.

Note that we explicitly set all preprocessor defines to a value, instead of just defining or undefining them. Now that these 4 defines are set throughout the whole framework, in a uniform way, we can easily check for these values whenever we encounter a dependency.

A couple of extra defines are derived from the four mentioned above. In many cases, e.g. cases were we have both target- and host-endianness dependencies, we want to have a way to check whether the two endiannesses are the same or different. Therefore we add one more preprocessor define, SWAP\_ENDIANESS. This define is set to 1 when the endiannesses are different, and set to 0 when they are the same. Since converting from little to big endianness is the same as converting from big endianness to little, this define comes in handy whenever we have encounter a structure that is both dependent on the host and the target platform's endianness.

Endianness in files on disk can be divided in two variants. One variant is a file that contains target-dependent information. This includes the serial binary and the parallel binary. The other variant is a file that does not contain target-dependent information, like the profiling files of the back-end. These files are always stored in a big-endian way. To process structures in files that have a target-endianness dependency, and of course implicitly also a host-endianness dependency, we now can use the SWAP\_ENDIANESS define to read and write these files correctly. To process files that only have a host-endianness dependency, we can use the HOST\_BIG\_ENDIAN or its inverse, the HOST\_LITTLE\_ENDIAN define.

More problematic are files that contain both target-dependent data (apply target-endianness) and target-independent (apply host-endianness) data. The serial binary, for instance, also contains various structures that have nothing to do with the program, but are necessary for a correct

binary. Care must be taken that the routines that operate on these files can recognize the various structures and process them correctly. The approach taken is to have all host-endianness dependencies written out in big-endian on disk. This corresponds with the format on disk that the legacy tools used. The target-endianness is stored either little or big endian, and a tag (in this case the binary-header) is used to differentiate between the two forms of target-endianness.

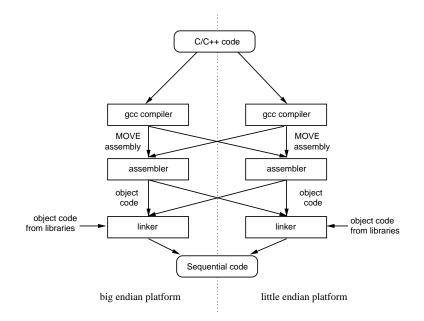

To visualize the cross platform requirements on the front-end, please look at figure 4.1. This will show that every step in the process should be able to read either output from a platform with the same endianness, as well as output from a platform with a different endianness. This figure shows the trajectory for one target-endianness. To list all possible cross-relationships, one should duplicate this figure for another target-endianness. These two figures, each representing a target-endianness, then would be completely unrelated. For example, a linker compiled to link big-endian move code cannot read little-endian move code.

Figure 4.1: The front-end on both endianness platforms

# 4.2 The MOVE front-end

The front-end consists of the GCC compiler, version 2.7.0, and the bintools distribution, version 1.38, together with a standard BSD C-library. All three components can be made endianness independent on their own, as long as the interface format is clearly defined. We have three interface formats that we have to deal with:

- 1. plain text assembly code (.s files)

- 2. non-linked object files (.o files)

- 3. linked binaries (no suffix)

Regarding host-endianness dependencies, we impose the requirement on these two latter formats that they are independent of the host-endianness. This results in the property that a file can be created on one platform, and read back by another platform, without any problems.

The first format, the plain text assembly, has no host-endianness dependencies, since it is plain text. Plain text is stored sequentially on disk, and has no endianness at all. The other two do have dependencies, because the object format deploys both bit-fields as well as byte-ordering within a word.

Regarding target-endianness dependencies, we impose the requirement on these three formats that the binary formats all use the same encodings, so that there is no format difference between the data in an object and the data in a binary. This also makes sure that object files archived in a library can be linked against other object files without worrying whether a certain routine came from a stand-alone object file or a library.

Target-endianness can be divided up in two parts: The actual instructions and the helper information, such as the symbol table and the relocation table. The choices made for the various types of endianness for these various kinds of data inside an object file, will be further explained in subsection 4.2.2, which deals with the port of the assembler, linker and binary tools.

#### 4.2.1 GCC

Since GCC version 2.7.0 is already host-endianness independent, no code changes were needed. Target-endianness is controlled by some directives in the so called "target-description macros", as defined the the machine.h file of GCC. The relevant macros are BITS\_BIG\_ENDIAN, BYTES\_BIG\_ENDIAN and WORDS\_BIG\_ENDIAN [Sta94]. For little-endian targets, all three defines are set to zero, and for big-endian targets all three defines are set to one.

Since GCC outputs plain text .s-files, the assembly doesn't need to care about most endianness problems. A word will be represented as its decimal equivalent in ASCII, and it's the assembler's job to encode this in 4 bytes. What does matter is bitfields within a byte, which will be implemented by the compiler by shifting the byte several bits, as well as accessing bytes within a word explicitly in C. This is also handled by the compiler by outputting code that shifts a word several bytes in order to be able to access the right byte in a word. All the compiler needs is the three above-mentioned switches to take care of these cases. This concludes the port of both the target-endianness as well as the host-endianness dependencies of the GCC compiler.

#### 4.2.2 Assembler, linker and auxiliary binary tools

The version of the bintools<sup>1</sup> used in the MOVE framework is version 1.38. This is unfortunately a very old version, and completely obsolete. There are two major drawbacks with this version: The architecture format is not easily changed, instead, for each port, a complete implementation of the tools exist, instead of a configurable plugin, like GCC-2.7.0 or the newer versions of bintools. The second drawback is that host-endianness independence is not implied, like it is in GCC-2.7.0 or the newer versions of bintools.

These considerations led to a feasibility study of deploying a newer version of the tools. A new version of the bintools distribution was inspected, but porting to the existing MOVE binary format, while preserving all intermediate formats and the actual serial binary that the

<sup>&</sup>lt;sup>1</sup>the common name for the group of assembler, linker and other tools

back-end can read, would be a lot of work. On the other hand, some work on making these tools host-endianness aware was already in progress. Conclusion was that a complete new port to the MOVE binary format would require more work than changing the current code base. Therefore it was decided the current version 1.38 was to be changed.

The binary tools consist of the following programs:

- as, the assembler

- ld, the linker/loader

- ar, the library archiver

- size, a utility to print segment sizes

- nm, a utility to print out symbols

- objdump, a utility to dump various segments

- ranlib, a utility to index a library archive

- dem, a utility to demangle C++ symbols

- c++-filt, another utility to demangle C++ symbols

- strip, a utility to strip a binary from its symbols

These tools can be divided in three parts, the assembler, the linker and the rest of the tools.

#### 4.2.2.1 The assembler

The assembler was very straightforward to port. The function md\_number\_to\_chars is responsible for placing a value representing a byte, halfword or word in a file stream. It does this by putting each byte in the correct position in the 4-byte word. For this it uses the C++ >> operator, which is already host-endianness safe (the compiler will recognize that operator and rearrange bytes and words in order to let the >> operator be endianness-independent). So the only consideration is the target endianness. By adding a check for TARGET\_LITTLE\_ENDIAN it was trivial to put the bytes on the right spot in the word, according to the rules of endianness.

The function md\_number\_to\_chars is, amongst others, called from the routine that emits the text segment. Since the move binary instruction field encoded in the binary file contains bitfields, the calls to md\_number\_to\_chars are re-ordered in case of a little endian target.

#### 4.2.2.2 The linker

The linker needs to actually read all various segments of an object, in order to be able to read the symbol and relocation tables, alter them and write them back into the final binary. Since this old version of ld processes all sections with direct calls to the Unix system call to read(2) and write(2), it was not directly possible to swap various bitfields and bytes. These functions read a whole block at once into a buffer, without the option to swap while reading. Therefore for every kind of segment, new routines called read\_<segment> and write\_<segment> are created to be put in place of the actual read(2) and write(2) calls. These hooks then read the corresponding segment in a buffer, process that buffer for endianness according to the HOST\_LITTLE\_ENDIAN and TARGET\_LITTLE\_ENDIAN predefines, as explained in chapter 3.1, and return the buffer to the calling routine.

In this fashion, the following routines are defined to serve as hook for the real read(2) and write(2) calls:

- read\_header, for the binary header

- read\_integer, for a simple number

- read\_symroot, for symbol table indexes

- read\_symbols, for symbols

- read\_symdef, for symbol definitions

- read\_reloc, for relocation information

- read\_arhdr, for the archive header

- read\_text, for the text segment

- read\_strings, for simple strings of text

Also, their write\_counterparts are defined.

These functions read or write the corresponding segment, with knowledge on where bitfields and other boundaries (such as 16 bit data that only needs to be swapped on half-word boundaries) on segments occur, so they can apply the endianess switches correctly.

#### 4.2.2.3 Bintools

The bintools, coming from the same distribution as the linker in the previous section, suffer from the same drawback that they deploy direct calls to read(2) and write(2). In addition to this, they also use direct calls to fread(3) and fwrite(3). This means that the list presented in the previous section needs to be duplicated to also be able to hook all calls to fread(3) and fwrite(3). For the rest, the port of these bintools is straightforward and implies, just as with the linker, replacing all occurrences to read(2), write(2), fread(3) and fwrite(3) with calls to their corresponding hooks.

## 4.2.3 System libraries

The GNU C Library is endianness independent, except at one point. There are different ways of encoding floating point numbers. They are:

- 1. vax for the VAX D\_floating format

- 2. tahoe for the TAHOE double format

- 3. **national** for IEEE machines whose floating point implementation has similar byte ordering as the NATIONAL 32016 with 32081

4. ieee for other IEEE machines

A comparison with floating point implementations on other architectures learned that bigendian IEEE machines use the "ieee" format, while little-endian IEEE machines use the "national" format. The makelibs script that generates the libm library, the math part of the C-library, was changed so that when the libraries were compiled for a little-endian MOVE target, the "national" encoding would be used.

## 4.3 The MOVE back-end

The back-end communicates with the front-end through only one thing, namely the binary. As explained in the previous section, the host-endianness of the platform where the framework runs on does not matter, only the target-endianness of the MOVE architecture will influence the contents of the binary.

Also, it was noted that tools could be run from any host platform. That means files written to disk between runs of various parts of the back-end should be host-endianness independent, too. The files we are dealing here with are:

- 1. the serial binary that is produced by the front-end

- 2. profiling data that is written to disk

- 3. the parallel binary that is produced by the scheduler

- 4. the parallel assembly that is produced by the scheduler

Subsection 4.3.1 will deal with the reading of the serial binary, subsection 4.3.2 with the scheduling of the MOVE code, subsection 4.3.3 will deal with the profiling files and subsection 4.3.4 will deal with the write of the parallel binary. The parallel assembly file is just plain text and has no endianness dependencies.

#### 4.3.1 Binary reader

The binary reader is, endianness-wise, the trickiest part of the back-end. It has the task of reading the binary generated by the GNU front-end and convert it into internal data structures. With respect to endianness, this means two things:

- 1. The binary must be read independent from the **host endianness**. That means that in parts where there is no target-endianness dependency, the define HOST\_LITTLE\_ENDIAN must be checked, and a byte swap must occur if the host endianness is different from the endianness of the structure on disk (which is always big endian, like it was in the legacy framework).

- 2. The binary must be read independent from the **target endianness**. That means that in parts where there is a target-endianness dependency, the define SWAP\_ENDIANNESS must be checked, and a byte swap must occur if the host endianness is different from the endianness of the structure on disk (which can be either way, depending on the target architecture).

As mentioned in subsection 4.2.2, the serial binary contains various different sections. The class AOut takes care of reading in the binary, section by section. The following structures needed adaptation on endianness

- the header, which contains bitfields. The header does not contain any target-dependent code, so only HOST\_LITTLE\_ENDIAN is checked for the bitfields. However, the assembler output routines swap everything. As discussed during the front-end discussion, the md\_numbers\_to\_chars is called for every segment, even the segments that contain no target-dependent information. This is because of the old version of the assembler. Therefore we still need a SWAP\_ENDIANESS check on the whole header, also on the parts that do not contain any target-endianness dependencies.

- the text and data parts are both host and target endianness dependent. Therefore these are read in using the SWAP\_ENDIANESS directive. The moves themselves are stored as bitfields in a word, so we need to guard them with a HOST\_LITTLE\_ENDIAN check and swap accordingly.

- the relocation data is stored on disk, independent of the target, always in big-endian format., therefore only HOST\_LITTLE\_ENDIAN is checked. Inside the relocation data, we also have to deal with bitfields, so also on those bitfields a HOST\_LITTLE\_ENDIAN check is required.

- the symbols data are stored as strings on disk. These strings are endianess independent. The only caveat here is that the symbol also contains a word with bitfields. This word needs a SWAP\_ENDIANESS check. (not a HOST\_LITTLE\_ENDIAN check like other bitfields, since the whole data is not swapped on byte ordering during read, as the other are)

Concluding we can say that in general, only target-dependent data like the text and data segments, are both checked against host and target dependencies. Therefore we have to guard these reads with a SWAP\_ENDIANESS. Other non-target related data need only to be guarded with HOST\_LITTLE\_ENDIAN. Bitfields, however, must be also checked against host endianness at all times. This check is implemented by changing the declaration of the structure at compile-time to match the bitfield-ordering of that specific endianness.

#### 4.3.2 Scheduler

The scheduler is responsible for taking the internal data-structure representing the serial binary, and converting it into another data-structure that represents the parallel binary. This involves various steps but none of these steps work on the actual data in the binary. Values like addresses are already put in the data structures in a correct way by the binary reader, and the binary writer is responsible for converting the structures back into a binary. Therefore, the scheduling algorithms do no need any adaptations with respect to endianness dependencies.

#### 4.3.3 Simulator

Simulation generates profiling information, like frequency count and memory dependencies. This profiling data can be written to disk to be used in subsequent runs of the scheduler or simulator. Therefore care must be taken when writing and reading these files. The routines Prog::SaveProfile,Prog::ReadProfile,Prog::LoadMDeps, Prog::SaveMDeps and Prog::MDepsExists are therefore guarded with checks on HOST\_LITTLE\_ENDIAN to make sure the profiling data is written to disk in a host independent fashion (namely big-endian), so profiling data can be used across platforms.

The simulator itself does not operate on files. It, however, has other dependencies on endianness. The simulator has to make sure it can offer the program under simulation an environment that is a correct image of the actual target platform. This means that parts of the simulator that represent a feature of the target platform, like the memory, the register files, the buses, have a target-endianness dependency. Most parts, however, have only one way to access them, e.g. register files and buses can only be written to by whole words at once, without the possibility to access smaller parts of these words. If one wants a smaller part of a register, this would already have been addressed in the actual move assembly, that the GCC front-end has generated correctly already. In other words, these components of the target architecture are word-addressable and nothing else.

The memory is the big exception here. Memory, although usually written to in whole words, is byte-addressable. Also, the MOVE architecture provides operations to access half-words and bytes in memory. This means every write or read to or from memory needs to be split up in bytes, which will then be written to the memory in a fashion depending on the target-endianness of the architecture.

Specifically, the memory class SimMem has member functions like SimMem::WriteW, SimMem::WriteH, SimMem::WriteB, SimMem::WriteS and SimMem::WriteD for respectively writing words, halfwords, bytes, single-precision floats and double-precision floats. Also, their read-counterparts are present. These functions all work by first getting a whole 32bit quantity from memory, then byte swap depending on the SWAP\_ENDIANESS predefine, and either read or write the correct (part of a) word. The implementation of the SimMem class can be found in appendix A.

#### 4.3.4 Binary writer

The binary writer's job is to convert the internal data structure of the program into two files: a readable assembly output, usually called b.txt, and a parallel binary, suitable for feeding to an actual chip, called b.out. The data structures itself have no endianness dependencies, and the assembly output is plain text. The focus here lies on the parallel binary.

We assume that by setting the target endianness, we also specify the bit-order of the instruction stream. This means that if we write out a little-endian binary, both the byte-ordering in the instruction word (which can be fairly large, e.g. 128 bits for PcomP), and the bit-ordering per byte is little endian.

For the implementation this means, that we have to make the routine that outputs the so called BitArray endianness aware. The BitArray represents the actual move instruction word bits. This routine is the OutputBinary(ostream &os, Insn \*insn) routine. This routine is responsible for allocating the BitArray. Class BitArray is already overloaded with the << operator. The change is that this overload function is altered to make it target-endianness aware, so that it can bit-swap the entire instruction word, if necessary.

# 4.4 Conclusions

The port of the MOVE framework to be both host and target-endianness independent is completed with success. The tools compile without any compile time options given on both big and little-endian hosts. The distribution is altered so that one compile-time switch will make both the front-end as the back-end target-endianness aware. This distribution then can be installed in a parallel directory tree on the same machine and a simple change to the shell's default search path can let the tools switch between the little and big-endian targets.

# Part III

# Immediates

# 5

# Immediates overview

A large part of this thesis is devoted to the issue of encoding immediates in the MOVE processor. In this chapter, an introduction on immediates in MOVE is given. In section 5.1 and 5.2 and general overview on immediates and their implementation in other architectures is given, and in section 5.3 the current state of immediates in MOVE is given. The next two chapters will deal with the implementation of the new immediate framework and a review on the implemented code.

# 5.1 What are immediates

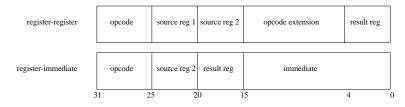

A processor usually has different ways to supply operands to its operations. Usual ways include register reference mode (add r3, r1, r2) and immediate mode (add r3, r1, #234).

An immediate is a way to pass a constant value directly from the instruction stream to an operation in the processor. To encode an immediate in the instruction stream, caution has to be taken. An immediate can take up relatively many bits of the instruction word, e.g. you only need 5 bits to encode 32 registers, but you need already 10 bits to be able to specify, e.g. constant 911. If you want to do an add of two constant 32bit values into a register, you need to encode, apart from the result register, 64 additional bits. To handle the encoding of large immediates into the instruction stream, different architectures have come up with different solutions.

Encoding immediates in the instruction stream poses several problems:

- As already mentioned, the code size will increase, since constants take a lot of bits, especially compared to (efficient) encodings for the address space for registers.

- If the immediate bits are separated from the operation that uses them, scheduling becomes

more difficult.

• We can distinguish between signed and unsigned immediates. Care has to be taken when sign-extending immediates to fit a certain immediate field.

# 5.2 Immediates in other architectures

Before we discuss the implementation of immediates, we will describe how other common architectures have solved the problem of immediates.

#### 5.2.1 CISC

As an example on how a typical CISC machine has solved the immediate problem, we'll take the x86 instruction set as an example. The actual name CISC ("Complex Instruction Set Computer") indicates that its instruction set can be very specific and large. A common feature of CISC is that is has many different addressing modes. We'll take the example of the x86 "ADD" [Int97] instruction here, and list all possibilities of using this "ADD" instruction with an immediate operand.

| Opcode | Instruction    | Description      |

|--------|----------------|------------------|

| 04 ib  | ADD AL, imm8   | Add imm8 to AL   |